### ՀԱՅԱՍՏԱՆԻ ՀԱՆՐԱՊԵՏՈՒԹՅԱՆ ԿՐԹՈՒԹՅԱՆ ԵՎ ԳԻՏՈՒԹՅԱՆ ՆՈՒՈՐՈՐՈՒԹՅՈՒՆ

ՀԱՅԱՍՏԱՆԻ ԱԶԳԱՅԻՆ ՊՈԼԻՏԵԽՆԻԿԱԿԱՆ ՀԱՄԱԼՍԱՐԱՆ

# ՍԱՀԱԿՅԱՆ ԱՐԹՈՒՐ ՍՏԵՓԱՆԻ

ՄՈՒՏՔ/ԵԼՔ ՀԱՆԳՈՒՅՑՆԵՐԻ ԱՇԽԱՏԱՆՔԱՅԻՆ ՌԵԺԻՄՆԵՐԻ ԿԱՅՈՒՆԱՑՄԱՆ ՄԻՋՈՑՆԵՐԻ ՄՇԱԿՈՒՄՆ և ՀԵՏԱԶՈՏՈՒՄԸ

Ե.27.01 «Էլեկտրոնիկա, միկրո և նանոէլեկտրոնիկա» մասնագիտությամբ տեխնիկական գիտությունների թեկնածուի գիտական աստիձանի հայցման ատենախոսության

# ՄԵՂՄԱԳԻՐ

Երևան 2017

МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РЕСПУБЛИКИ АРМЕНИЯ

НАШИОНАЛЬНЫЙ ПОЛИТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ АРМЕНИИ

# СААКЯН АРТУР СТЕПАНОВИЧ

РАЗРАБОТКА И ИССЛЕДОВАНИЕ СРЕДСТВ СТАБИЛИЗАЦИИ РАБОЧИХ РЕЖИМОВ УЗЛОВ ВВОДА-ВЫВОДА

#### **АВТОРЕФЕРАТ**

диссертации на соискание ученой степени кандидата технических наук по специальности 05.27.01 — "Электроника, микро- и наноэлектроника"

Ереван 2017

Ատենախոսության թեման հաստատվել է Հայաստանի պետական Ճարտարագիտական համալսարանում (Պոլիտեխնիկ)։

Գիտական ղեկավար՝ տ.գ.դ., պրոֆ. Վ.Շ. Մելիքյան

Պաշտոնական ընդդիմախոսներ՝ տ.գ.դ., պրոֆ. Ռ.Ռ. Վարդանյան,

տ.գ.թ., դոց. Խ.Գ. Շառոյան,

Առաջատար կազմակերպություն` ՀՀ ԳԱԱ Ռադիոֆիզիկայի և

էլեկտրոնիկայի ինստիտուտ

Ատենախոսության պաշտպանությունը տեղի կունենա 2017թ. մայիսի 5-ին, ժամը  $14^{00}$ -ին, 2ԱՊ2-ում գործող «Ռադիոտեխնիկայի և էլեկտրոնիկայի» 046 Մասնագիտական խորհրդի նիստում (հասցեն՝ 0009, Երևան, Տերյան փ., 105, 17 մասնաշենք):

Ատենախոսությանը կարելի է ծանոթանալ ՀԱՊՀ– ի գրադարանում։ Սեղմագիրն առաքված 2017թ. մարտի 31-ին։

046 Մասնագիտական խորհրդի գիտական քարտուղար, տ.գ.թ.

A Stato-

Մ.Ց. Ալվազյան

Тема диссертации утверждена в Государственном инженерном университете Армении (Политехник)

Научный руководитель: д.т.н., проф. В.Ш. Меликян

Официальные оппоненты: д.т.н., проф. Р.Р. Варданян

к.т.н., доц. Х.Г. Шароян,

Ведущая организация: Институт радиофизики и электроники АН

Армении

Защита диссертации состоится 5-го мая 2017 г. в 14<sup>00</sup> ч. на заседании Специализированного совета 046 — «Радиотехники и электроники», действующего при НПУА, по адресу: 0009, г. Ереван, ул. Теряна, 105, корпус 17. С диссертацией можно ознакомиться в библиотеке НПУА. Автореферат разослан 31 марта 2017 г.

Ученый секретарь Специализированного совета 046, к.т.н. М.Ц. Айвазян

Malo

#### ОБЩАЯ ХАРАКТЕРИСТИКА РАБОТЫ

<u>Актуальность темы.</u> Известно, что масштабирование интегральных схем (ИС) способствует повышению их производительности и увеличению концентрации элементов на полупроводниковых кристаллах (ПК). Однако имеется и ряд других проблем, решение которых может привести не только к упрощению процесса разработки ИС, но и к росту надежности произведенных ИС и повышению их универсальности.

Спрос на высокую скорость процесса приема, обработки и передачи данных все чаще и чаще негативно влияет на стабильность режимов работы ИС. В частности, уменьшилась амплитуда, увеличилась степень искажения сигналов, падения напряжения в шинах питания, взаимодействия сигналов, а также повысилась зависимость параметров функциональных узлов ИС от технологических процессов, напряжения источника питания и температуры окружающей среды (ПНТ).

Учитывая важность этих вопросов, ведущие компании в этой отрасли в последние годы осуществили ряд работ с целью ослабления зависимости параметров ИС от ПНТ. Тем не менее эти решения не в полной мере отвечают современным требованиям.

Стали актуальнымы уменьшения степени зависимости параметров ИС от ПНТ. Причина заключается в том, что в случае каких-либо отклонений ПНТ удовлетворение требований разработки усложняется и, следовательно, повышается стоимость разработки ИС.

Меры по увеличению устойчивости параметров особенно важны для узлов ввода/вывода (ВВ), так как они обеспечивают связь между ИС и внешним миром и наоборот.

Параллельно с увеличением жесткости требований к параметрам устройств ВВ появились проблемы, связанные не только с компенсацией отклонения от ПНТ, но и с усложнением обеспечения устойчивости их работы в разных режимах.

Диссертационная работа посвящена обеспечению стабильности параметров быстродействующих узлов BB от различных рабочих режимов и ПНТ.

<u>Объект исследования.</u> Самокорректирующие системы узлов ВВ и способы стабилизация их параметров.

<u>Цель</u> работы. Целью диссертационной работы является разработка и исследование средств стабилизации параметров узлов ввода-вывода независимо от рабочих режимов, технологических процессов, напряжения источника питания и температуры окружающей среды.

Методы исследования. При выполнении работы были использованы способы построения объектно-ориентированного программного обеспечения (ПО) и архитектурные решения цифровых, аналоговых и аналого-цифровых сигнальных схем.

#### Научная новизна:

1. Разработаны принципы построения универсальной и самокорректирующей системы задержки с обратной связью, обеспечивающие за счет использования нескольких элементов задержки

- существенно широкий диапазон частоты по сравнению с известными решениями.

- 2. Создан метод координации сопротивления, обеспечивающий без использования стабильного элемента вне ПК необходимую погрешность калибровки сопротивления с существенно меньшей площадью на ПК и энергопотреблением.

- 3. Предложены схемотехнические решения коррекции коэффициента заполнения, обеспечивающие за счет самокоррекции значительно меньшую погрешность коэффициента заполнения (КЗ) по сравнению с существующими решениями.

- 4. Разработан метод регулировки временных запасов, обеспечивающий за счет самокоррекции независимо от ПНТ необходимые запасы времен установки и удержания и исключающий дражение сигналов.

- 5. Создан способ, исключающий дополнительные потери энергии в системах со многими источниками питания, который за счет увеличения занимаемой на ПК площади обеспечивает значительное сокращение потерь энергии, вызванных в результате отключений источников питания.

#### На защиту выносятся следующие научные положения:

- метод координации сопротивления без использования стабильного элемента вне полупроводникового кристалла;

- принцип самокорректирующей системы задержки с обратной связью и с широким диапазоном частоты;

- способ, исключающий дополнительные потери энергии в системах с многими источниками питания;

- схемотехнические решения коррекции коэффициента заполнения.

- метод регулировки временных запасов настроек и удержания.

<u>Практическая ценность работы</u> Практическая ценность работы в том, что по сравнению с существующими решениями, в настоящем исследовании:

- увеличен частотный диапазон системы задержки с обратной связью на 95%;

- обеспечены необходимые временные запасы установки и удержания вне зависимости от ПНТ между синхросигналом и информационным сигналом (не менее ~88 пс);

- достигнута коррекция КЗ вплоть до 50±1% за счет потребления тока до ~2,3 мА с применением дифференциального усилителя (ДУ) и до ~2,3 мА в случае отсутствия ДУ.

- получен стабильный элемент на ПК с точностью до ~5,1%, обеспечивающий меньшее энергопотребление (от 12 до 70%) и существенно меньшую площадь на кристалле;

- снижены потери энергии до ~98% в системах со многими источниками питания во всех режимах выключения источника питания;

- разработано программное обеспечение IO Designer, позволяющее существенно снизить сложность разработки упомянутых систем.

<u>Достоверность научных положений</u> достигнута математическими обоснованиями, а также результатами экспериментов на основе схемотехнического моделирования.

**Внедрение.** Программное обеспечение IO Designer внедрено и широко используется в компании ЗАО "Синопсис Армения". Оно предназначено для проектирования, анализа результатов моделирования и коррекции параметров стабильных узлов ВВ.

<u>Публикации.</u> Основные положения диссертации представлены в 14 научных работах, список которых приведен в конце автореферата.

Структура и объем работы. Работа состоит из введения, трех глав, основных выводов, списка литературы, включающего 138 наименований, и 4 приложений. Основной текст работы составляет 119 страниц, включая 84 рисунка и 7 таблиц. Общий объем работы, включая приложения, составляет 139 страниц. Диссертация написана на армянском языке.

#### ОСНОВНОЕ СОДЕРЖАНИЕ РАБОТЫ

**Во введении** обоснована актуальность темы диссертации, сформулированы цель и задачи исследования, представлены научная новизна, практическая значимость и основные научные положения, выносимые на защиту.

<u>В первой главе</u> представлены текущие требование к ИС, такие как универсальность, что вызвано необходимостью систем, работающих в различных рабочих частотах. В частности, наличие многочисленных специальных устройств (USB, PCIe, SATA, HDMI, DP, XAUI и т.д.) ВВ ведет к потреблению универсальных узлов в этих системах. Этим способом сокращаются время проектирования микросхем и затрата ресурсов.

Помимо различных устройств приема-передачи, работающих в стандартных рабочих частотах, каждое из них в отдельности может работать в разных рабочих режимах, что предполагает различные рабочие частоты.

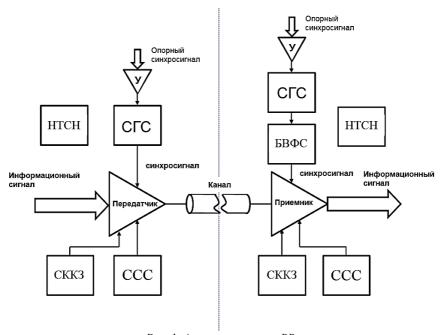

Классический узел ВВ представляет собой средство передачи и приема данных. Он состоит из узлов приема и передачи и, конечно же, опорных узлов, которые снабжают эти два узла различными опорными сигналами (рис. 1).

Основным узлом является система генератора синхросигнала (СГС), которая получает уже улучшенный опорный синхросигнал, синтезирует высокоскоростной синхросигнал для узлов передатчика и приемника, а система корректировки коэффициента заполнения (СККЗ) корректирует КЗ этих сигналов.

Следующий опорный узел — это независимый от температуры стабилизатор напряжения (НТСН), обеспечивающий питание и опорное напряжение в узлах приема-передачи вне зависимости от температуры. Работа этого узла основана на свойствах биполярного транзистора. Известно, что падение напряжения между терминалами транзистора база-эмиттер имеет обратную зависимость от температуры, т.е.  $V_{\rm 69}$  (база-эмиттер) напряжения уменьшается с увеличением температуры.

Наложение этой зависимости с положительной зависимостью приводит к стабильному напряжению, которое практически не зависит от температуры.

Сигнал, проходя по каналу, отражается и искажает полезный сигнал, что и служит причиной ненадежного считывания данных. Основной причиной этого явления является несоответствие сопротивлений. Система соответствия сопротивлений (ССС) координирует выходные сопротивления передатчика и входные сопротивления приемника с сопротивлением канала, которое определяется стандартом данного ВВ.

Поскольку синхросигнал не поступает в передающий узел, его необходимо получить с такой фазой, с которой можно надежно считывать сигнал входной даты. Блок восстановления фазы синхросигнала (БВФС), основываясь на фазе даты сигнала, отклоняет фазу синхросигнала, идущего с СГС, и получает нужную для чтения фазу сигнала.

Рис. 1. Архитектура узла ВВ

Показаны необходимость регулирования сигналов в передатчике и приемнике, а также причины появления ошибки КЗ в узлах ВВ и важность их корректировки. Не менее важной задачей является необходимость повышения временных запасов настройки удержания синхросигнала в узлах ВВ и регулировки сигнала в передатчике и приемнике, подробное описания которых дается в первой главе.

В узлах ВВ важнейшей проблемой являются утечки тока из-за отключения питания в различных рабочих режимах.

**<u>Во второй главе</u>** представлены разработанные методы решения проблем, изложенных в первой главе.

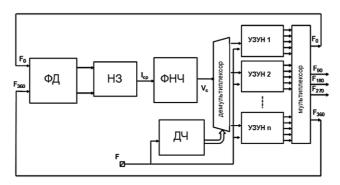

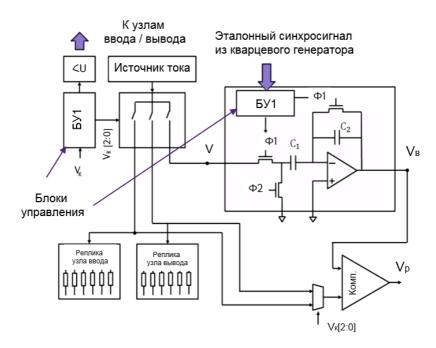

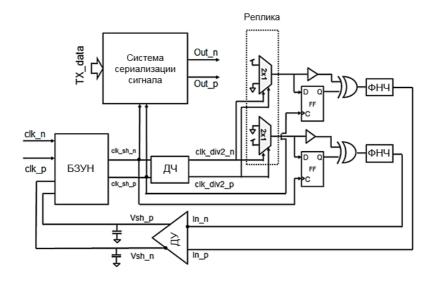

Метод увеличения устройств задержки с самокорректированием частотной полосы с обратной связью. Представлен метод увеличения устройств задержки самокорректированием частотной полосы с обратной связью (УЗОС) (рис. 2), который обеспечивает частотную полосу в диапазоне (1 кГц...8 ГГц), что больше на ~95%, чем в известных решениях, и полностью соответствует всем известным стандартам устройств ВВ. Система имеет максимальное время подстройки ~640 нс за счет прибавления площади ~15...20% и мощности ~10%, которые соответствуют требованиям такого типа схем.

Рис. 2. Архитектура предложенного УЗОС

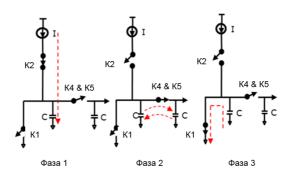

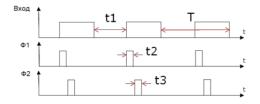

Детектор частот (ДЧ) состоит из двух узлов. Приоритетный опорный сигнал применяется к входу преобразователя частота-напряжение (ПЧН), затем полученное напряжение (уров. 1,2) с помощью аналого-цифрового преобразователя (АЦП) преобразуется в цифровой код. Работа ПЧН состоит из трех фаз (рис. 3,4)

Рис. 3. Рабочие фазы ПЧН

Рис. 4. Временные диаграммы блока управления ПЧН

$$V_{\text{BbIX}} = \frac{I \cdot t1}{C2} \tag{1}$$

$$V_{\text{BbIX}} = \frac{I*T}{2*C2} = \frac{I}{2*f*C2} \tag{2}$$

Из выражение (2) следует, что напряжение выходного сигнала ПЧН ( $V_{\rm BMX}$ ) зависит только от частоты входного сигнала (f), поскольку величина тока I постоянная.

Минимальная и максимальная входные частоты ПЧН определяются уравнениями:

$$F_{\text{MMH}} = (I/2*C) * (1/V_{\text{Make}})$$

(3)

$$F_{\text{Marc}} = (I/2*C)*(1/V_{\text{MHH}})$$

(4)

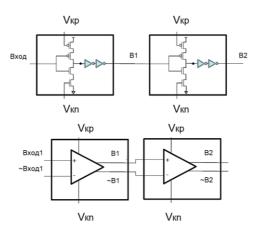

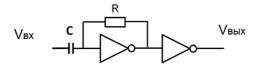

В предложенном УЗОС используются два типа ячеек задержки (ЯЗ). Одна ячеека состоит из каскадов инверторов, а другая - из дифференциальных усилителей (рис. 5).

Рис. 5. Архитектуры ЯЗ, используемые в предложенном УЗОС

Метод коррекции сопротивления без использования внешнего элемента со стабильными параметрами. Система корректировки сопротивления (СКС) (рис. 6), предлагаемая в диссертации, по сравнению с известными из литературы решениями, имеет следующие преимущества:

- предлагаемая СКС занимает на ПК ~21% меньше площади по сравнению с СКС, имеющуей внешний стабильный элемент;

- система универсальна, поскольку совместима с разными стандартами систем BB:

- система полностью самокорректирующая и дает возможность периодической коррекции;

- 4. система не имеет внешнего стабильного элемента, что дает возможность избежать внешних воздействий и ошибок.

Рис. 6. Архитектура предлагаемой СКС

Таким образом спроектированная СКС для передатчика и приемника обеспечивает перечисленные преимущества, но по сравнению с методом со

внешним стабильным элементом, она имеет на  $\sim 3\%$  меньшую точность и на  $\sim 12\%$  большее энергопотребление.

Полученные результаты (табл. 1) полностью соответствуют стандартам ряда устройств ВВ, таким как универсальная последовательная шина (USB) и межсистемная связь вычислительных узлов (PCIe).

Таблица 1 Результаты моделирования СКС

| Варианты                           | Код         | Точность    | Погрешность   |

|------------------------------------|-------------|-------------|---------------|

| моделирования                      | регулировки | регулировки | сопротивления |

|                                    | (#)         | (%)         | (%)           |

| Типовой-типовой (55 °C)            | 25          | 3,8         | 0,7           |

| Быстрый-быстрый (–40 °C)           | 23          | 1,1         | 4,5           |

| Медленный-<br>медленный<br>(125°C) | 30          | 2,3         | 5,1           |

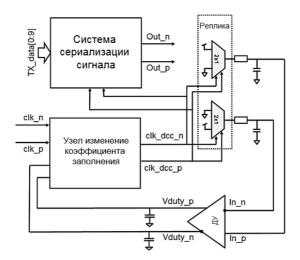

Методы коррекции коэффициента заполнения синхросигнала с употреблением операционного усилителя и без него. Разработаны два типа систем коррекции КЗ.

Первая архитектура (рис. 7) в отрицательной обратной связи содержит ДУ, с помощью которого сигналы с КЗ 58% и 42% скорректированы до  $\sim 49,25\%$  и 50,78% при максимальной потребляемой мощности  $\sim 2,3$  мА.

Во втором типе системы (рис. 8) ДУ не применен. Он после коррекции обеспечивает КЗ до  $50\pm1\%$ . По сравнению с архитектурой с ДУ, эта версия употребляет на  $\sim\!80\%$  меньше электроэнергии и занимает на  $\sim\!35\%$  меньше площади.

Недостаток системы в том, что ее верхняя рабочая частота ограничивается диапазоном  $2.5...3~\Gamma\Gamma$ ц, а максимальная рабочая частота системы с ДУ достигает  $5.5...6~\Gamma\Gamma$ ц.

Таким образом, СККЗ без ДУ (рис. 8, 9) совместима со многими стандартами узлов ВВ, потребляет меньше энергии и площади, чем версия с усилителям, но ограничена максимальной рабочей частотой.

Рис. 7. Блок-диаграмма СККЗ с ДУ

СВКЗ – система вычисления КЗ ФНЧ – фильтр низких частот

Рис. 8. Структура СККЗ без ДУ

Рис. 9. Схема вычисления коэффициента заполнения

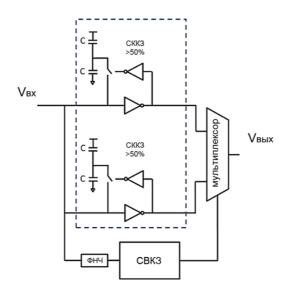

# Метод регулировки и стабилизации временных запасов настроек и удержания. Предложена новая система регулировки и стабилизации временных запасов настроек и удержания (рис. 10), которая независимо от ПНТ обеспечивает правильные временные фазы между сигналом синхронизации и информацией.

БЗУН – блок задержки управляемой питанием

Puc. 10. Архитектура системы регулировки и стабилизации временных запасов настроек и удержания

В качестве опорных для системы регулировки и стабилизации временных запасов настроек и удержания выступают выходные сигналы системы фазовой автоподстройка частоты (clk\_p \( \text{l} \) clk\_n). В итоге на выходе системы получаются сигналы с правильными фазами (clk\_sh\_p \( \text{l} \) clk\_sh\_n) по отношению к фазам

сигнала информации, обеспечивающие максимальные временные запасы настроек и утверждения.

В результате разработана новая система, которая совместима с современными устройствами узлов последовательного ВВ и обеспечивает независимо от ПНТ и с методом самокорректирования регулирование запасов временных интервалов между сигналами информации и синхронизации. Обеспечение необходимых временных запасов приводит к исключению дрожания сигналов и уменьшению информационных ошибок при передаче данных.

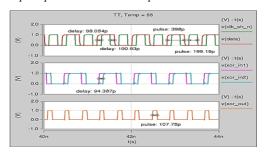

Система передачи данных на частоте 5 Гбит/с обеспечивает по меньшей мере от  $\sim$ 88 пс запасов настройки и от  $\sim$ 89 пс запасов утверждения (рис. 11, 12), что полностью соответствует ограничению стандартных узлов последовательного BB, таких как USB2.0 и USB 3.0 ( $\geq$ 20 пс), за счет увеличения площади до  $\sim$ 12% и энергопотребления до  $\sim$ 14%. Предлагаемая система позволяет также сократить время, затрачиваемое на проектирование, до 70 %.

Рис. 11. Пример недостаточного временного запаса настройки

Рис. 12. Временные диаграммы сигналов после коррекции предлагаемой системы регулирования и стабилизации временных запасов настроек и удержания

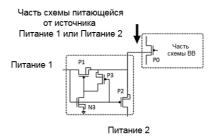

Метод, исключающий дополнительные потери энергии в системах со многими источниками питания. В устройствах ВВ, имеющих более одного источника питания, с целью энергосбережения возникает необходимость отключения некоторых источников питаний в разных рабочих режимах.

При проектировании больших систем очень трудно учитывать потери при отключении некоторых источников питания, которые происходят в различных конфликтных частях. Поэтому необходимо разработать метод (рис. 13), который сразу же после выключения питания способом самокорректирования соединит конфликтные точки схемы с другими источниками питаниями и, таким образом, исключит потери энергии.

Рис. 13. Структура защитной системы

Предложен метод, помогающий предотвратить дополнительные потери энергии системы с несколькими питаниями, который может использоваться в разных режимах отключения питания. Данный метод также соответствует технологии комплементарной структуры металл-оксид-полупроводник (КМОП) и может быть использована в разных стандартах узлов ВВ с энергосберегающими режимами. В худшем случае система обеспечивает уменьшение потери энергии до ~98% (табл. 2).

Таблица 2

Результаты моделирования предложенной системы

| Варианты моделирования          | Ток утечки без<br>предложенной<br>системы (мкА) | Ток утечки с<br>предложенной<br>системой (нА) |

|---------------------------------|-------------------------------------------------|-----------------------------------------------|

| Типовой-типовой<br>(55 °C)      | 0,25                                            | 4,2                                           |

| Быстрый-быстрый<br>(-40 °C)     | 2,7                                             | 20                                            |

| Медленный- медленный<br>(125°C) | 0,21                                            | 1,8                                           |

<u>В третьей главе</u> представлено разработанное программное обеспечение для реализации предлагаемых решений и архитектур, позволяющее упростить работу разработчика и ускорить время разработки.

Предлагаемое ПО дает возможность проектировать и проводить необходимые анализы для систем, представленных во второй главе диссертации.

Программное средство может быть также использовано для масштабирования и регулировки параметров схем в случае перехода с одного технологического процесса к другому, а также — для передачи параметров. Оно позволяет также оценить энергопотребление проекта и дать предварительную оценку занимаемой площади схемы.

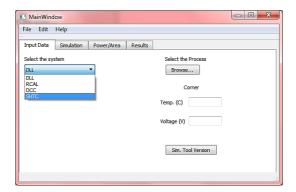

Программа IO Designer предназначена для процесса разработки и проектирования и имеет удобный интерфейс для разработчика. В течение короткого периода времени можно ввести необходимые входные данные и затем выполнить моделирование.

Основное окно программы изображено на рис. 14. Оно состоит из четырех главных околлек:

- 1. Input Data секция для входных данных системы.

- 2. Simulation секция для моделирования.

- 3. Power/Area Estimation секция для предварительной оценки энергопотребления и площади

- 4. Results секция для результатов.

Puc. 14. Основное окно программы IO Designer

Раздел "Input Data" предлагаемого программного обеспечения состоит из четырех подразделов. Установка выбора узла корректировки осуществляется с помощью поля "Select the System", где присутствуют версии "DLL", "Rcal", "ДКК" и "SHTC".

# ОСНОВНЫЕ ВЫВОДЫ ПО ДИССЕРТАЦИОННОЙ РАБОТЕ

- Разработан принцип самокорректирующей системы задержки с широкой полосой частоты, которая за счет употребления нескольких элементов задержки обеспечивает полосу рабочей частоты в диапазоне 1 кГц...8 ГГц, что на ~70% больше по сравнению с существующими решениями.

- 2. Создан метод координации сопротивления, который без использования стабильного элемента обеспечивает сопротивление с точностью до ~5,1% и меньшее энергопотребление от 12 до 70% по сравнению с существующими решениями вне полупроводникового кристалла.

- Предложены схемотехнические решения коррекции коэффициента заполнения (КЗ), которые за счет самокорректирующих методов с использованием дифференциального усилителя (ДУ) и без него обеспечивают КЗ заполнения вплоть до 50 ±1%, за счет потребления тока до ~2,3 мА с употреблением ДУ и до ~ 2,3 мА без ДУ.

- 4. Разработан метод регулировки временных запасов, который за счет самокорректирования и независимо от технологических процессов, напряжения источника питания и температуры окружающей среды (ПНТ) регулировки временных запасов исключает дрожание и обеспечивает необходимые временные запасы настройки и удержания между синхросигналом и сигналом информации (не менее чем ~88 пс).

- Создан способ, исключающий дополнительные потери энергии в системах со многими источниками питания, который за счет увеличения используемой площади поверхности полупроводникового кристалла обеспечивает сокращение потерь энергии, вызванных отключениями источников питания, до ~98 %.

- 6. Предлагаемые решения и методы использованы в средствах программного обеспечения разработки ввода-вывода ІО Designer. Средства программного обеспечения широко используются в компании ЗАО "Синопсис Армения" для упрощения процесса проектирования устройств ввода-вывода. Испытание программы ІО Designer показало, что время, затраченное на процесс проектирования и на подготовку исходных данных удалось уменьшить примерно в 10 раз. Благодаря внедрению предложенных методов и за счет максимально потребляемой энергии до ~25% и увеличения занимаемой площади до ~20% становятся возможными повышение универсальности устройств ввода-вывода и их разработка в других технологических процессах.

# Основные результаты диссертации опубликованы в следующих работах:

- Sahakyan A.S., Hayrapetyan A. G., Dingchyan H. H., Architecture of Self-Configurable Delay-Locked Loop by Frequency Range // Proceeding of the 9th International Conference of Semiconductor Micro and Nano Electronics.-2013.- P. 203–206.

- Melikyan V., Sahakyan A., Piloyan M., et al., Resistance Calibration Method Without External Precision Elements // Proceedings of IEEE East-West Design & Test Symposium (EWDTS'2013), Kharkov National University of Radioelectronics.- Rostov-On-Don, Russia, 2013.- P. 24–27.

- 3. Melikyan V.Sh., Sahakyan A. S., Hayrapetyan A. G., et al., Serializer/Deserializer Output Data Signal Duty Cycle Correction Method // Proceedings of 57th IcETRAN Conference, Zlatibor, Serbia, 2013.- EL3.4.1-4.

- Melikyan V.Sh., Sahakyan A. S., Shishmanyan A. H., Data Clock Setup and Hold Times Margins Correction Methods in High Speed Serial Links // Proceedings of 9th International Conference CSIT 2013 (Computer Science and Information Technologies).- 2013.- P. 356–359.

- 5. **Sahakyan A. S.,** Architecture of Gain-Boosted Fully Differential OTA with Rail-to-Rail Inputs // Proceedings of 9th International Conference CSIT 2013 (Computer Science and Information Technologies).- 2013.- P. 360–363.

- Melikyan V.Sh., Sahakyan A. S., Safaryan K. H., et al., High Accuracy Equalization Method for Receiver Active Equalizer // Proceedings of IEEE East-West Design & Test Symposium (EWDTS'2013).- Rostov-on-Don, Russia.- 2013.- P. 390–393.

- Melikyan V., Sahakyan A., Piloyan M., High Accuracy Self-Configurable DLL by Frequency Range // Proceeding of the 1st International Conference on Electrical, Electronic and Computing Engineering IcETRAN.- 2014.- P. 237– 230.

- 8. V.Sh. Melikyan, A. S. Sahakyan, Dingchyan H. H., et al., Low Voltage Current mirror with a High Output Voltage Swing // Известия НАН РА и ГИУА. Серия Техн. наук. 2014. -Т.67, N 2. С. 165–172.

- 9. **Melikyan V.Sh., Sahakyan A. S., Poghosyan S. M., et al.,** High PSRR Gain-Boosted Rail-To-Rail OTA // Proceeding of the 5th Small Systems Simulation Symposium, Serbia. 2014. P. 16–19.

- Melikyan V.Sh., Sahakyan A. S., Sahakyan A. S., et al., High PSRR and Accuracy Receiver Active Equalizer // Proceeding of IEEE 34th International Conference electronics and nanotechnology ELNANO.- Kyiv, Ukraine.- 2014.-P. 230–233.

- Hekimyan A., Sahakyan A., Trdatyan D., Capacitor Mismatch Correction Method in Pipeline ADCs // Proceedings of IEEE East-West Design & Test Symposium (EWDTS'2015), Kharkov National University of Radioelectronics.- Batumi, Georgia.- 2015.- P. 43–46.

- 12. Melikyan V., Sahakyan A., Shishmanyan A., et al., Low Power Duty Cycle Adjustment Simple Method in High Speed Serial Links // Proceedings of IEEE East-West Design & Test Symposium (EWDTS'2015), Kharkov National University of Radio-electronics.- Batumi, Georgia.- 2015.- P. 43–46.

- 13. **Melikyan V., Sahakyan A., Shishmanyan A.,** Multi-Rate Clock-Data Recovery Solution in High Speed Serial Links // Proceeding of IEEE 35th International Conference electronics and nanotechnology ELNANO.- Kyiv, Ukraine.- 2015.- P. 242–244.

- 14. **Sahakyan A. S.,** Self-Decision Power Collapsing Protection System // Հայաստանի Ազգային Պոլիտեխնիկական Համալսարանի Լրաբեր. Գիտական հոդվածների ժողովածու.- Երևան, 2016.- էջ 279–283.

#### ገፈይወበውበህ

Հայտնի է, որ ինտեգրալ սխեմաների (ԻՍ) մասշտաբավորումը նպաստում է ԻՍ-երի արտադրության ելքի տոկոսի բարձացմանը, կիսահաղորդչային բյուրեղի (ԿԲ) վրա տարերի խտության մեծացմանը և այլն։ Սակայն առկա են նաև մի շարք այլ խնդիրներ, որոնց լուծումները կարող են հանգեցնել, ոչ միայն ԻՍ-երի նախագծման գործընթացի պարզեցմանը, այլն արտադրված ԻՍ-երի աշխատանքի հուսալիության և դրանց համապիտանելիության աՃին։

Տվյալների ընդունման, մշակման և փոխանցման գործընթացների ավելի ու ավելի արագագործ լինելու պահանջը բացասական ազդեցություն է գործել ԻՍ-երի աշխատանքային ռեժիմների կայունության վրա։ Մասնավորապես, մեծացել են ազդանշանի մարման կամ աղավաղման չափերը, լարման անկումը սնման դողերում, փոխազդեցությունները, ինչպես նաև ԻՍ-երում ֆունկցիոնալ հանգույցների պարամետրերի խիստ կախվածությունները տեխնոլոգիական գործընթացից, սնման լարումից և արտաքին միջավայրի ջերմաստիձանից (ԳԼՋ)։ ԳԼՋ-ից ԻՍ-երի պարամետրերի կախվածության աստիձանի փոքրացումը ներկայումս դարձել է արդիական։ Պատձառն այն է, որ բարդացել է ԳԼՋ-ների ցանկացած շեղման դեպքում նախագծումը։

Հաշվի առնելով նշված հիմնահարցի կարևորությունը, այս ոլորտի առաջատար ընկերությունները վերջին տարիներին իրականացնում են մի շարք աշխատանքներ, որոնք նպատակաուղված են ԳԼՋ-ից ԻՍ-երի պարամետրերի կախվածության աստիձանի փոքրացմանը։ Սակայն այդ լուծումները լիովին չեն բավարարում առկա պահանջներին։

Կայունություն ապահովող միջոցները հատկապես կարևոր են ԻՍ-երի մուտք/ելք հանգույցների պարագայում, քանի որ վերջիններս ապահովում են ԻՍ-երի միջուկի կապր արտաքին միջավայրի հետ և հակառակը։

Մուտք/ելք (U/Ե) սարքերի վրա դրված պահանջների խստացումներին զուգընթաց առաջացել է, ոչ միայն ԳԼՋ-ով պայամանավորված շեղումերը չեզոքացնող լուծումների, այլև տարբեր աշխատանքային ռեժիմներում հանգույցի պարամետրական կայունության ապահովման անհրաժեշտություն։

Ատենախոսությունը նվիրված է արագագործ մուտք/ելք հանգույցների ԳԼՋ-ի և տարբեր աշխատանքային ռեժիմներում պարամետրերի կայունություն ապահովման հիմնահարցերի լուծմանը։

Աշխատանքի ընթացքում մշակվել է ինքնակարգաբերվող և համապիտանի լայն հաձախականային շերտով հապաղման հետադարձ կապով սարք, որը մի քանի հապաղման տարրերի կիրառման շնորհիվ, ապահովում է 1 ԿՀց -ից մինջն ~8 ԳՀց հաձախականային շերտ, ինչը ~70 %-ով մեծ է առկա լուծումների համեմատ։ Մտեղծվել է դիմադրությունների

համաձայնեցման եղանակ, որը արտաքին կայուն պարամետրերով տարրի չօգտագործման հաշվին, ապահովում է առկա լուծումների համեմատ 12-ից 72 %-ով պակաս էներգասպառում, բավարար՝ ~5,1 % կարգաբերման սխալանք և էապես փոքր մակերես։

Առաջարկվել են լցման գործակցի ձշգրտման սխեմաներ, որոնք ինքնակարգաբերման ԴՈւ-ով lı առանց դրա օգտագործման ճարտարապետությունների կիրառման հաշվին ապահովում են առկա յուծումներին էապես գերազանցող պարամետրեր՝ առավելագույնը ~±0,78 % ԴՈւ-ով և ~±1 % առանց ԴՈւ-ի լցման գործակցի շեղում, մուտքային ազդանշանի ±8 % շեղման դեպրում։ Մշակվել է ժամանակների պաշարների ձշգրտման համակարգ, որը ինքնակարգաբերմամբ և անկախ ԳԼՋ-ից ժամանակային պաշարների ձշգրտման հաշվին բացառում է փոքր կարգման կամ հաստատման տևողություններից առաջացած թրթողոր, փոքրացնում է փոխանցված տվյալի սխալանքը և կրձատում նախագծման ժամկետը մոտ 70 %-nd:

Ստեղծվել է բազմասնուցումային համակարգերում լրացուցիչ Էներգասպառման կորուստները բացառող մեթոդ, որը ԿԲ-ի վրա մակերեսի ~5 մկմ²-ով մեծացման հաշվին ապահովում Է սնման լարումների անջատումներից առաջացած կորստի հոսանքների ~98 % նվազեցում։

Առաջարկված լուծումները և մեթոդները օգտագործվել են IO Designer ծրագրային գործիքում։ Ծրագրային միջոցը կիրառություն է գտել ՄԻՆՈՓՄԻՍ ԱՐՄԵՆԻԱ ՓԲԸ-ում և օգտագործվում է Մ/Ե սարքերի ենթահանգույցներ նախագծման և այլ բնույթի տարատեսակ գործընթացների պարզեցման նպատակով։ Ծրագրային միջոցի փորձարկման ընթացքում պարզ է դարձել, որ IO Designer միջոցը օգնում է մոտ 10 անգամ կրձատել նախագծման և մուտքային տվյալների նախապատրաստման վրա ծախսվող ժամանակը։ Առաջարկվող մեթոդների ներմուծման շնորհիվ ընդամենը էներգասպառման առավելագույնը ~25 %-ով և ԿԲ-ի վրա զբաղեցված մակերեսի ~20 % մեծացման արդյունքում հնարավոր է դառնում արդի Մ/Ե սարքերի ենթահանգույցները դարձնել ավելի համապիտանի նախագծման և այլ տեխնոլոգիական գործընթացում ներկայազման համար։

#### ARTUR STEPHAN SAHAKYAN

# RESEARCH AND DEVELOPMENT OF MEANS OF TRANSMITTER AND RECEIVER WORKING MODES STABILIZATION

#### **SUMMARY**

It is known that scaling of integrated circuits (IC) contributes to increase of yield and concentration of elements on semiconductor crystal (SC). But there are exist some other problems, which solving can brings either simplification of development of the IC or makes produced ICs more reliable and universal.

The requirements of data processing speeds negatively affecting into stability of IC performance. Especially, signal rejection and distortion, IR drop in supply nets, crosstalks and parameters dependency from process, voltage and temperature (PVT) become critical. As a result, nowadays, relaxing of parameter stability from PVT become actual problem. This come up because hard to meet the standard's specification over PVT variation.

Taking into account following problems, leading companies of this area in last years did various steps which relaxing IC parameters dependency from PVT. But this not fully enough to achieve target requirements.

PVT stability is especially important for input/output (I/O) devices, because they are providing connection between IC core and the external environment and which are interpretation of analog front end (AFE).

With requirement restrictions of I/O not just importance of parameter stabilization from PVT become critical. Parameters dependency from system different modes and rates comes up as well.

During investigation developed self-configurable delay-looked loop (DLL) with large frequency range, which due to several delay cell usage providing frequency range from 1kHz to  $\sim$ 8GHz, which by  $\sim$ 70 % bigger compere with current solutions. Also designed termination resistor calibration method, which due to not using external precision element compere with existing methods provides from 12 up to 72% low power consumption and  $\sim$ 5.1% calibration accuracy with essentially small area.

Proposed two duty cycle correction (DCC) methods, which using self-configuration technic with and without differential amplifier. DCCs compare with existing approach in a worst case corner with  $\pm 8$ % distortion in the inputs provides  $\sim\!\!\pm 0.78$ % with differential amplifier and  $\sim\!\!\pm 1$ % without it duty cycle error. Respect of setup/hold times stability designed setup/hold times margin correction method which helps to avoid jitter connected with low setup/hold time, decreasing data error probability and decreasing design/porting time up to 70%.

Another proposed approach is power collapsing protection system which helps to decrease current leakages and false DC paths in power collapsing cases and by  $\sim 5 \text{um}^2$  increasing area.

All proposed methods and approaches used in IO Designer application. It was applied in Synopsys Armenia CJSC and used to simplify design process of functional

blocks of I/O systems. During quality check of software concluded that its helps to decrease simulation setup and verification times by 10 times.

With proposed methods with just maximum  $\sim\!20$  % power consuption and  $\sim\!25$  % area increment it was real to increase portability and parameter stability from PVT and different modes.